STAC Report: New LDA/Xilinx solution under STAC-T0 (tick-to-trade network I/O)

Sub-30 nanosecond latency for 68-byte frames

1 June 2020

STAC recently performed STAC-T0 benchmarks on a stack utilizing the latest LDA MAC/PCS and TCP IP cores with a Xilinx FPGA and network adapter. The STAC Report is available here.

STAC-T0 uses accurate wire capture to measure the tick-to-trade network-I/O latency of any trading platform using UDP in, TCP out, and essentially no trading logic or market-specific protocol handling in between.

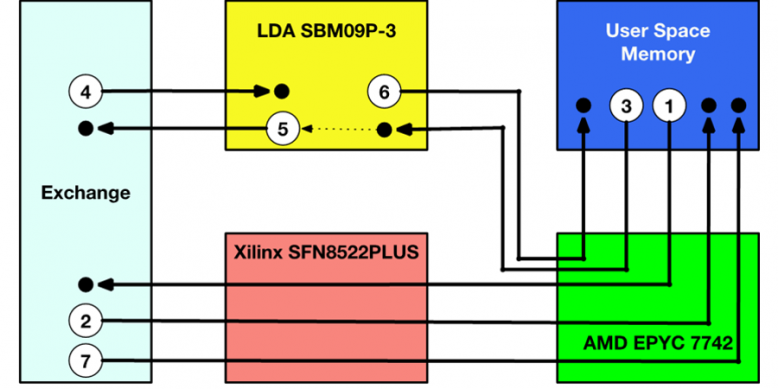

The "stack under test" (SUT) consisted of LDA Lightspeed TCP™ and16-bit MAC/PCS IP cores running in a Xilinx® Virtex™ UltraScale+ VU9P-3 FPGA on an LDA SBM09P-3 FPGA board in conjunction with Xilinx OpenOnload and a Xilinx SFN8522PLUS adapter, all hosted in a Lenovo ThinkSystem SR665 server with AMD EPYC™ 7742 processors.

Of the results, Xilinx and LDA chose to highlight the following:

- For 68-byte frames at all ingress rates, actionable latency had a minimum of 24.2 nanoseconds (STAC-T0.β1.*.B.ACTIONABLE.MIN)

- For 68-byte frames, actionable latency had a mean of 27.9 to 29.2 nanoseconds depending on ingress rate (STAC-T0.β1.*.B.ACTIONABLE.MEAN)

"Actionable" latency is the time from the last bit of inbound data needed to make a trading decision to the first bit of the simulated outbound order.

For details, please see the reports at the links above. Firms with subscripions to the Trade Flow STAC Track also have access to detailed test results for all message rates, message types, and latencies measured; the micro-detailed configuration information for the solution; and the test tools used in this project. To learn about subscription options, please contact us.

About STAC News

Read the latest about research, events, and other important news from STAC.