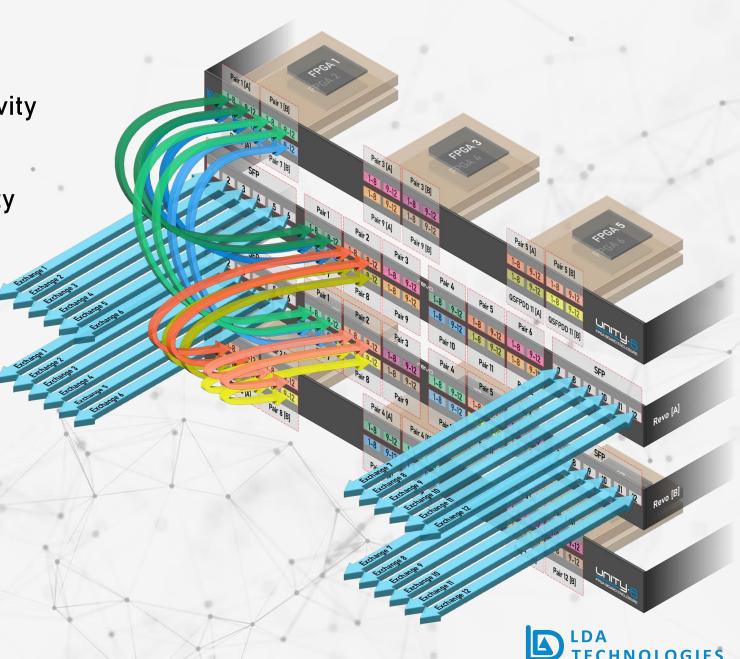

## Use Case

- Deliver the data from each line to 12 FPGA boards

- Enable each FPGA board to send data to any line

- At least 312 (?!) 10G links: 24 + 24\*12 = 312

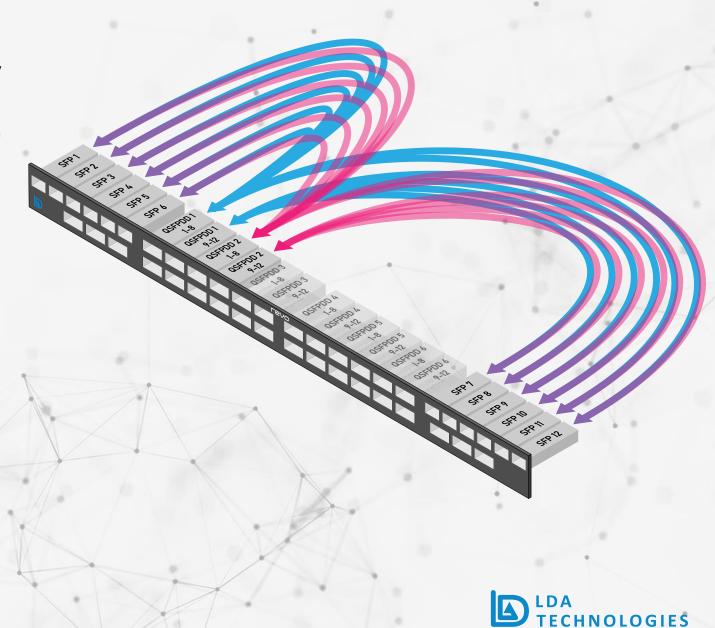

12x SFP+ ports for exchange connectivity

24x QSFPDD ports (12 port pairs) for downstream (FPGA board) connectivity

6x QSFPDD ports for housekeeping/management tasks or external timestamping/capture

• 12x SFP+ ports for exchange connectivity

24x QSFPDD ports (12 port pairs) for downstream (FPGA board) connectivity

6x QSFPDD ports for housekeeping/management tasks or external timestamping/capture

Configurable Layer 1 for SFP+ output

12x SFP+ ports for exchange connectivity

24x QSFPDD ports (12 port pairs) for downstream (FPGA board) connectivity

6x QSFPDD ports for housekeeping/management tasks or external timestamping/capture

Configurable Layer 1 for SFP+ output

Downstream interconnect with 2"-7" QSFPDD copper cables

- 12x SFP+ ports for exchange connectivity

- 24x QSFPDD ports (12 port pairs) for downstream (FPGA board) connectivity

- 6x QSFPDD ports for housekeeping/management tasks or external timestamping/capture

- Configurable Layer 1 for SFP+ output

- Downstream interconnect with 2"-7" QSFPDD copper cables

- Internal tap aggregation and timestamping option with the complete LDA NeoTap features for capture and monitoring purposes.