STAC Summit - November 2022

# What CXL means for FSI

Graham McKenzie Sr. Field Applications Engineer, Intel® Corporation

## New CXL protocol is game changing!!

# Matt's prediction is coming to fruition...

Dr. Matthew Grosvenor at Global STAC Live (Spring 2020)

in finance

## Introduction

Application/Workload Acceleration (Data transformation)

Infrastructure Acceleration (Processing of data in motion) Smart Storage/Memory (Processing of data at rest)

Choose best accelerator HW: CPUs, GPUs, AI, FPGAs, other chipsets

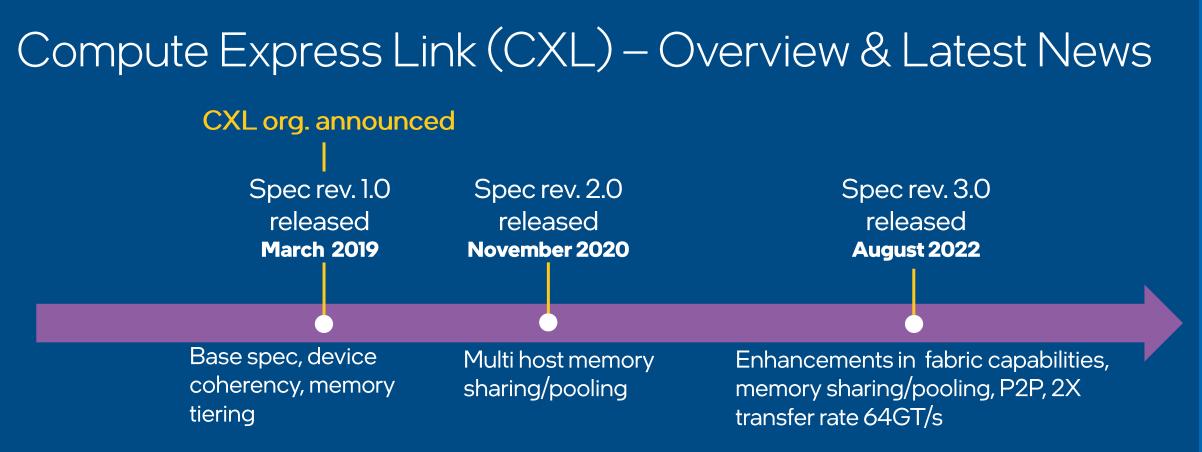

- What is CXL? An open-source coherent interconnect protocol (re-uses PCIe PHY/data layers)

- Who is in CXL.org? Over 200 members & growing

- Latest News:

- Gen-Z Consortium joined CXL & transferred assets/technology

- OpenCAPI Consortium letter of intent to join CXL

- CXL joins open fabric management frameworks (DMTF, OFA, SNIA)

https://www.computeexpresslink.org/

#### **CXL-based accelerators elevated to 1<sup>st</sup> class priority**

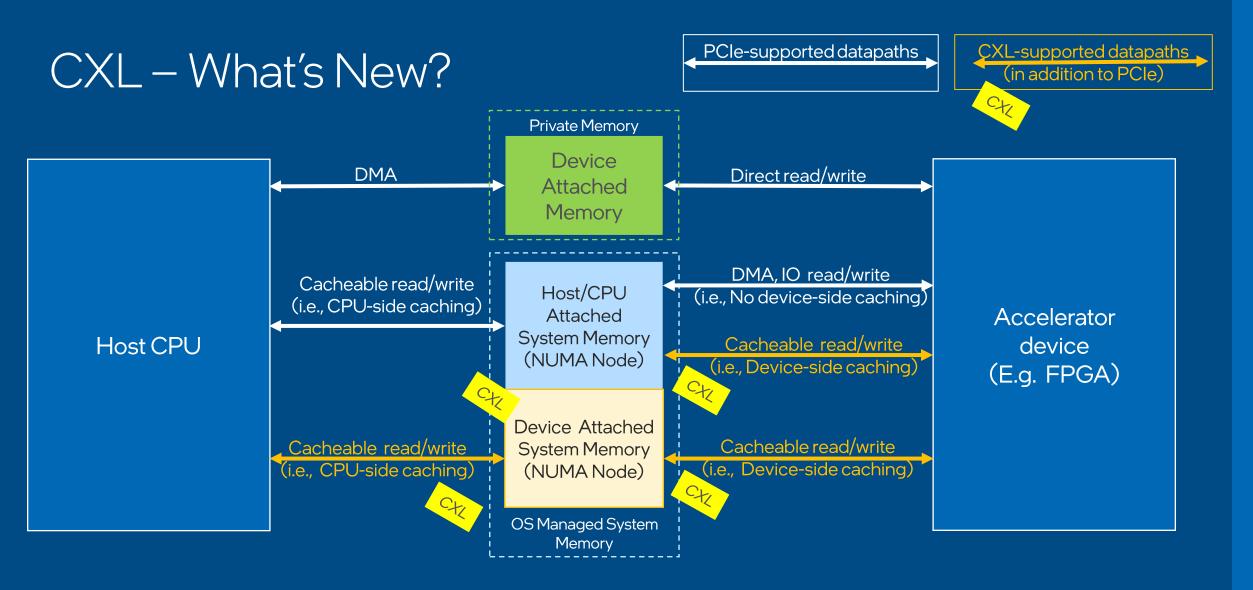

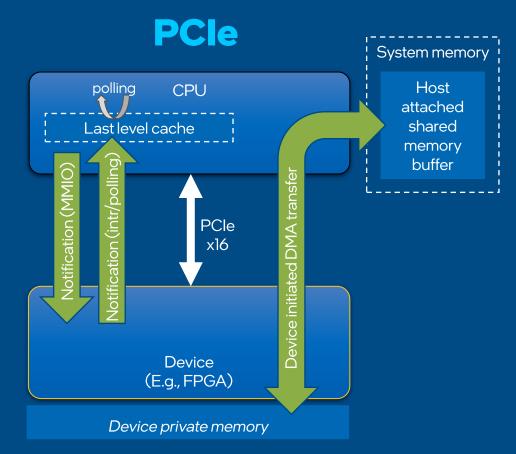

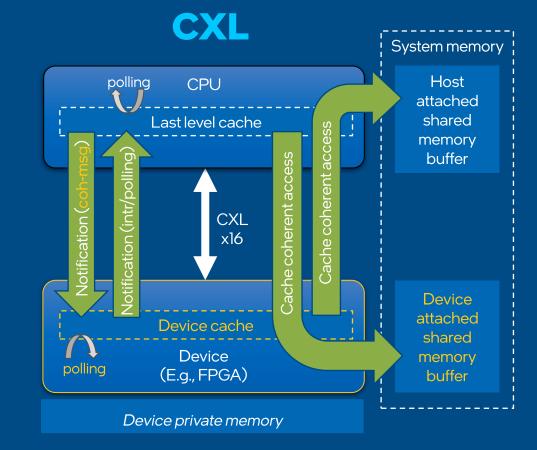

## CXL Accelerators – Common Shared Cache/Memory

#### CXL enables:

- Low latency notifications using coherency semantics (new)

- Device-side polling (new)

- Shared memory buffers cache coherently accessible by CPU and device (new)

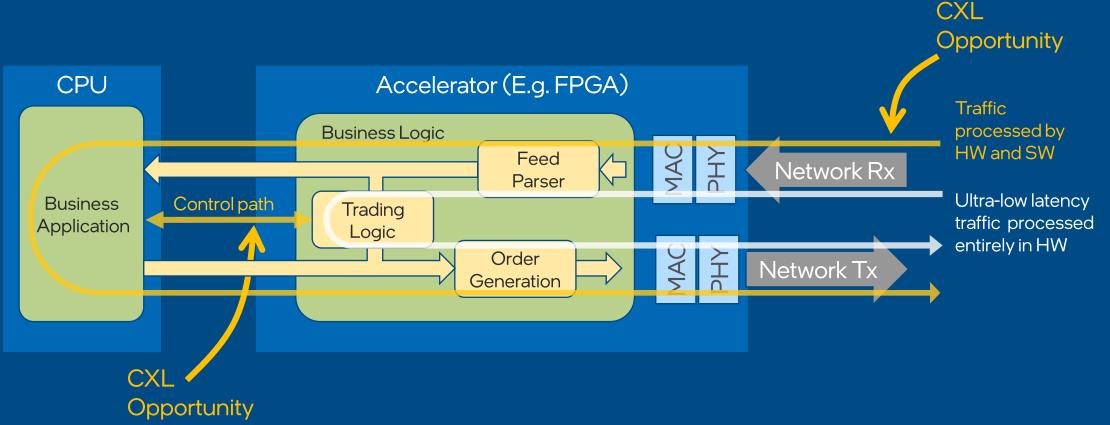

## Accelerating Securities Trading

CXL enables tightly coupled CPU-HW interactions, resulting in better use of CPU and hence helping reduce accelerator complexity

#### Intel<sup>®</sup> Agilex<sup>™</sup> FPGA

- 1st & only FPGA with CXL hard IP

- 4x higher CXL bandwidth per port vs. other FPGA CXL implementations<sup>1</sup>

- CXL 1.1 and 2.0 (see schedule)

<sup>1</sup>Learn more at www.intel.com/PerformanceIndex (see the FPGA section for workloads and configurations). Results may vary.

Intel Public

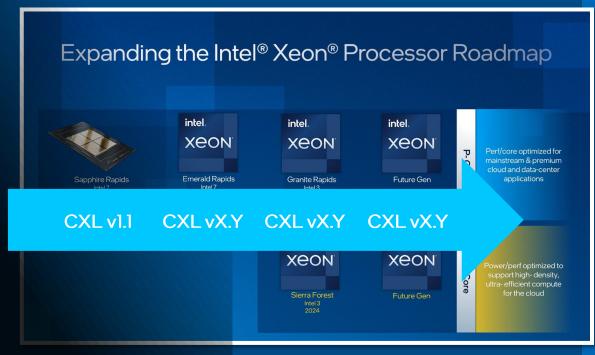

## CXL-Capable HW & Ecosystem

#### Contact OEM/ODM

- ✓ Server embargo release dates under CNDA

- Based on 4th Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable processor (formerly codenamed Sapphire Rapids)

#### Start CXL R&D now!

- ✓ Choose your production intercept

- ✓ Intel FPGA offers SW upgrade CXL 1.1 to 2.0

- Choose from a variety of Intel FPGA devices & board options

Source: Intel Investor Day (Feb. 17, 2022)

## Intel Agilex FPGAs – Leading Financial Services

#### Leadership with CXL

✓ 1<sup>st</sup> and only FPGA with CXL hard IP

✓ FPGA HW supports CXL 1.1 and 2.0

#### Strategic Collaboration with LMS

ÜberNIC<sup>™</sup> Exclusively Based on Intel Agilex FPGAs

Fully hardware network stack with CXL

Truly supports modern market data rates

intel. AGILEX<sup>®</sup>

Attend LMS session today

## Legal Notices and Disclaimers

- Performance varies by use, configuration and other factors. Learn more on the <u>Performance Index site</u>. Results may vary.

- Intel does not control or audit third-party data. You should consult other sources to evaluate accuracy.

- © Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. In the U.S. and/or other countries.

- \*Other names and brands may be claimed as the property of others.

- This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

- The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

- Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer to learn more at intel.com. Intel does not control or audit third-party data. You should consult other sources to evaluate accuracy.

- <sup>1</sup>Intel estimates based on Agilex FPGA CXL hard + soft IP test results (CXL link at Gen 5 x16) vs. Xilinx FPGA using 3rd party CXL soft IP (CXL link at Gen4x8), both interop with pre-production 4th Gen Intel Xeon processors.