# Mastering Ultra-Low Latency: The Technical Blueprint of FPGA and Software Hybrid Solutions

Presented by **Jean-François Gagnon**Ultra-Low Latency FPGA architect

October 2023

PREMIER

intel partner

# Architectural advantages of Hybrid Solutions

BALANCE THE FLEXIBILITY OF SOFTWARE-BASED SOLUTIONS AND THE PERFORMANCE OF HARDWARE-BASED SOLUTIONS

# Softwarebased solutions

- Lower cost

- Greater flexibility

- Optimal for prototyping and testing trading strategies

- Higher latency

- Lower performance

# Hardwarebased solutions

- Including ASICs, eFPGAs, and FPGAs

- High-performance processing

- Ideal for high-frequency trading with low latency and high throughput

- Less flexibility

### Hybridbased solutions

- Combine FPGA and software-based components

- FPGAs accelerate specific functions and algorithms while the CPU handles generalpurpose and complex trading algorithms

- Highly flexible, delivering very low latency performance

- Easy customizability

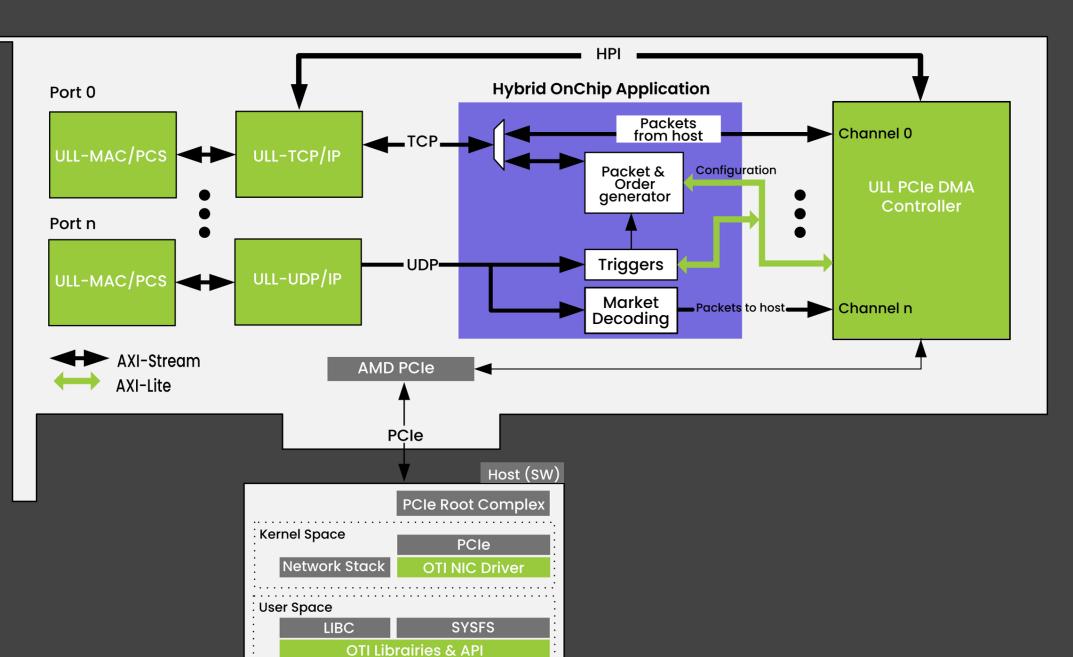

# ULL PCIe DMA Controller Hybrid Solutions

CUTTING-EDGE IP CORE ENABLING LIGHTNING-FAST BIDIRECTIONAL DATA TRANSFER BETWEEN THE HOST CPU AND FPGA

**User Application**

- Both FPGA and Host processor can send packets to TCP core

- Protocols not handle by the TCP and UDP cores are forwarded to Host processor through HPI channel

- Configurable parameters at build time:

- Number of channel

- Number of Queue on each channel

- Size of queues per channel

- Channel mode: synch or asynch.

- Latency optimized RTT around 640ns

NOT STAC BENCHMARKS

# ULL PCIe DMA Controller Software Tools

#### **ULL PCIe DMA Controller software description**

- Driver and library

- Linux kernel module provided with standard delivery packages (rpm, deb)

- Driver created to automatically detect PCIe card for early evaluation solution

- Library API easily handles buffer creation, transmission and reception

- Software tools

- Test application provided for latency measurement

- Application will configure and report measurement executed by FPGA application

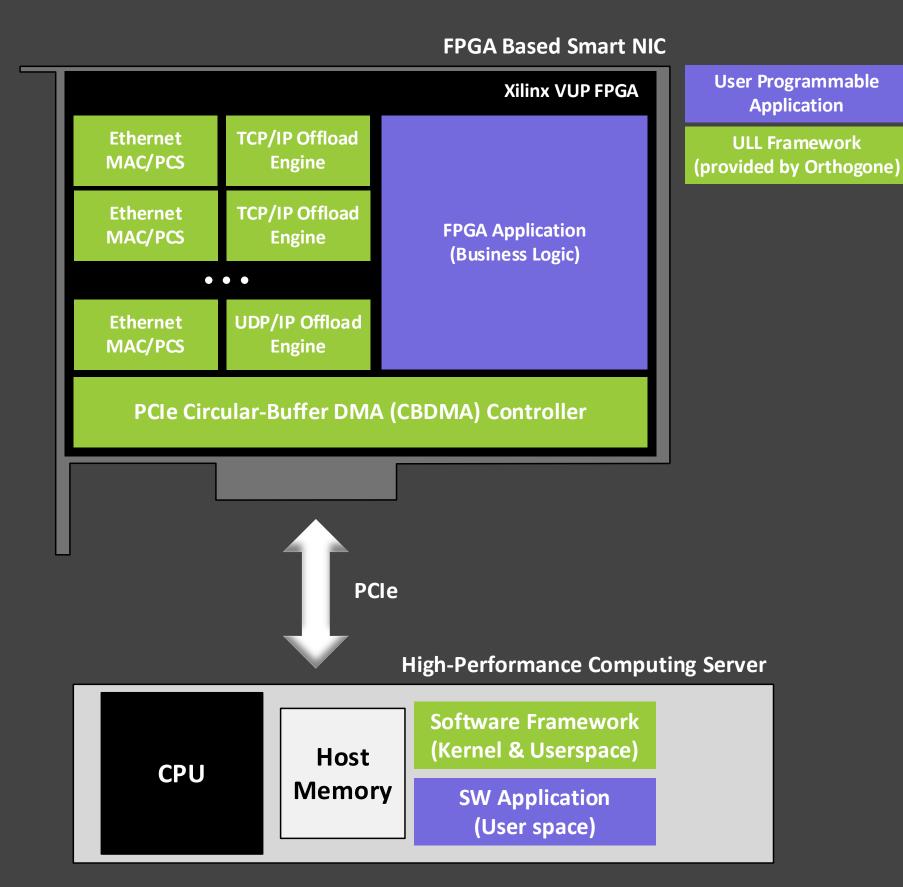

# FPGA IP Solutions Offering

ULTRA-LOW LATENCY NETWORKING SOLUTIONS

#### **ULL FPGA Framework**

- Best-in-class FPGA and SW solution to develop reconfigurable applications that require ultra-low latency performances.

- Specifically designed for trading applications

- Full suite of ULL FPGA IP cores

- FPGA Dev kit (design & simulation environment, reference design examples, debug tools, etc.)

- SW Framework (drivers, API, debugger, etc.)

#### ULL FPGA IP Cores

- Ethernet MAC/PCS (1 100G) with opt. RS-FEC

- TCP/IP Offload Engine

- UDP/IP Offload Engine

- PCIe Streaming DMA Controller

# ULL FPGA Framework

# Hardware Platforms

Can be ported on other UltraScale+ platforms

# Contact Information

Alex Raymond, Co-Founder, CTO <a href="mailto:araymond@orthogone.com">araymond@orthogone.com</a>

514.316.1917 x 703

# Orthogone Overview

Developers of the Seemingly Impossible

Orthogone offers highly specialized engineering solutions focused on the design of innovative products requiring in-depth knowledge of software development, embedded systems, FPGA and SoC.

95+

Multidisciplinary R&D Team 2007

Inception

Privately Held Headquartered in Montreal (Canada)

## **FPGA**

Solutions & IP Cores Technologies

#### **R&D Services**

- Systems engineering

- Software development

- Hardware design

- FPGA Design & Verification

#### **Key Industries**

- Datacenter & Comms

- Defense & Aerospace

#### **FPGA IP Portfolio**

- ULL FPGA Framework

- Ethernet MAC/PCS/FEC

- TCP/IP Offload Engine

- UDP/IP Offload Engine

- PCIe CBDMA Controller

#### **Ecosystem of Technology Partners**