THE POWER OF THE POSSIBLE<sup>TM</sup>

The Build vs Buy Dilemma Is A False Choice - Market Interaction

May 6, 2021

Shōganai

And

"!#"...

...We All See It

Every Day

The Status Quo Leaves You Exposed...

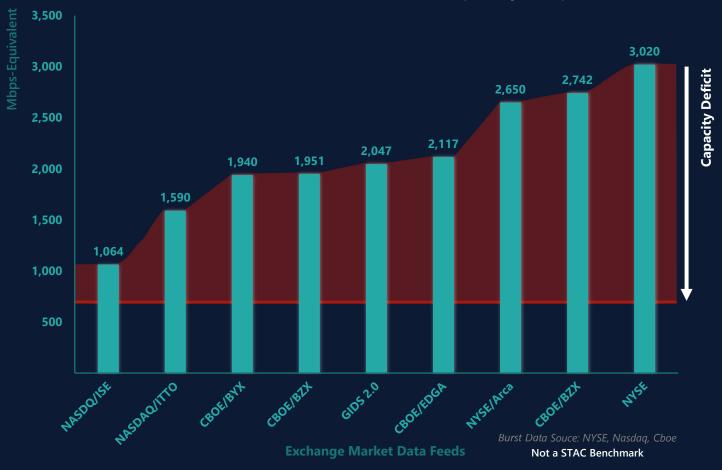

> Typical Market Data Burst Rates Cannot Be Handled

# 10GbE? Line Rate to Software Cannot Be Maintained

1ms Peak Market Data Burst Rate Capacity Requirements

Capability Limitations Bite At The Moment of Peak Risk/Reward

# Trading Stack Investment Yields Diminishing Returns

Tougher Than Ever...

...Buy vs Build Dilemma

- Today's Trading Stack is Expensive

- Equipment & People/Co-Lo Real Estate/Energy Usage

- Today's Trading Stack is Limiting

- Architecture Constraints/Multiple Hops/Unnecessary Latency

- Today's Trading Stack is Compromised

- Regulatory/Exchange/Broker Requirements

- Today's Trading Stack is Distracting

- Strategic Differentiation & Buy vs Build

Strategic Differentiation and Profitability Threatened

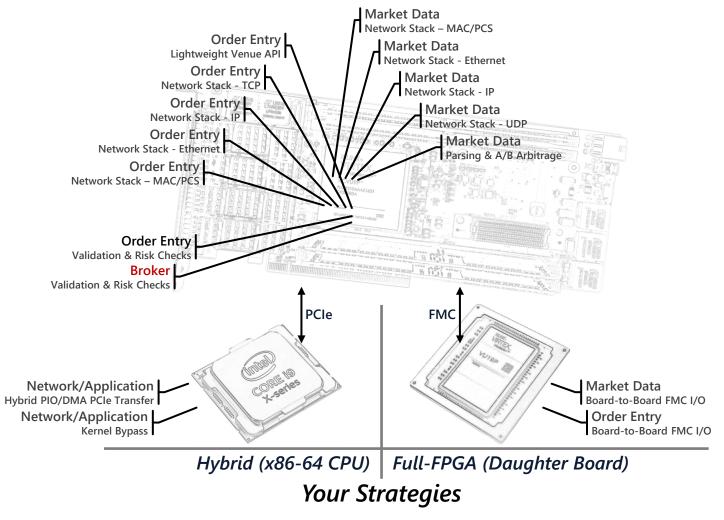

Naros.CCS™ Comprehensive Connectivity Solution...

> Modular Approach To Optimization

# Naros.CCS™ – Library of Functions

Network MAC/PCS

Trading

Multi-Dimension Queue

Network/Application

Stack, PCIe Transfer, & Kernel Bypass

Trading

Order Transmission

Network

Expanded Functionality

Trading

Lightweight Venue API

Packet

Capture & Replay

Trading

Market Data Parsing

Packet PTP & PPS

Trading

Validation & Risk Checks

Page - 4

Broker

Validation & Risk Checks

Note: Various Embodiments Above, Singly or in Combination, are Patented and/or Patent Pending

Library of Individual Functions Available Separately Or In Combination

# How To Optimize...

When Tools

Are Limited

By The Very

Constraints

They Should

Identify?

# Testing & Measurement Are Essential For Optimization

"Management of a system requires knowledge of the interrelationships between all of the components within the system..."

W. Edwards Deming

"If you can't measure it, you can't improve it."

Peter Drucker

Expose Bottlenecks...

Realistic

Burst & Stress

Testing of

Application/Network

Performance

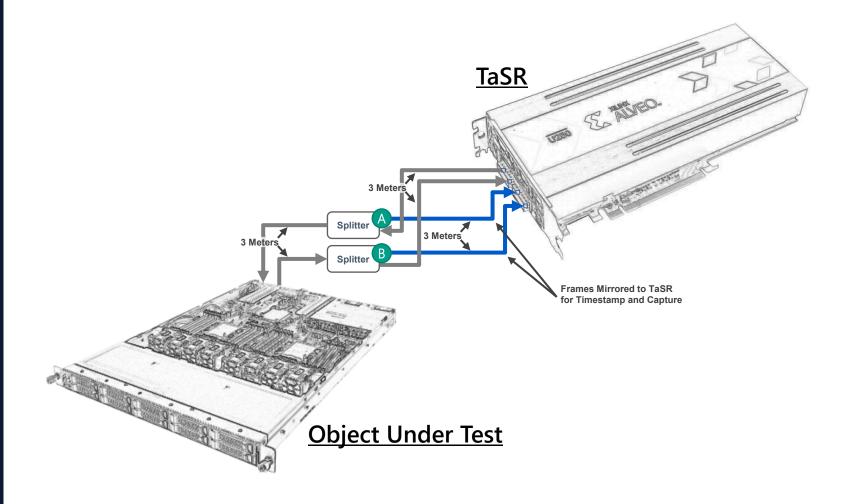

# TaSR™ - Hyper-Accurate Testing & Measurement

TaSR™ is an FPGA-Based <5ns-Precision Performance Measurement System

Not a STAC Benchmark

# TaSR™ - Hyper-Accurate Testing & Measurement

Expose Bottlenecks...

Realistic

Burst & Stress

Testing of

Application/Network

Performance

- RFC 2544 (Ethernet) Compliant Including:

- Throughput, Burstability, Latency, Frame Loss, System Recovery

- Non-RFC 2544 Functionality Including:

- Variable Delay, Packet Capture, Replay, Internal Clock Timestamp

- Layer 2 Start-Of-Frame FIFO, FILO, LILO Performance Measurements

- Configurable Traffic Generation (Protocol, Payload, Rate)

TaSR™ is an FPGA-Based <5ns-Precision Performance Measurement System

# Cut Through The BS...

...To Focus On Differentiation

# Trading Stack Investment Revisited

- Today's Trading Stack is Expensive

- Equipment & People/Co-Lo Real Estate/Energy Usage

- Today's Trading Stack is Limiting

- Architecture Constraints/Multiple Hops/Unnecessary Latency

- Today's Trading Stack is Compromised

- Regulatory/Exchange/Broker Requirements

- Today's Trading Stack is *Distracting*

- Strategic Differentiation & Buy vs Build

Deploy Your Resources To Focus On Differentiating Competitive Advantages

Modularity Brings...

Flexibility

For Today & Tomorrow

#### Naros.Card™

Seamlessly Supports Your Implementation – Whether Software or Hardware

Transforming

The

Trading

Stack...

Captures Alpha & Cuts OpEx Incrementally Or At Once

# Trading Stack Investment Revisited

|               |          |                                           | <b>Current Practice</b>                     | Inventing the Future - Naros.Card™6 |                          |

|---------------|----------|-------------------------------------------|---------------------------------------------|-------------------------------------|--------------------------|

|               |          |                                           | Software (x86-64)                           | Hybrid                              | Full FPGA                |

| Trading Stack | Internal | Trading<br>Strategy Processing            | CPU Cores Diverted                          | CPU Cores Reclaimed                 | CPU Dependency Ended     |

|               |          | Trading<br>Validation & Risk Checks       | 600ns to 1600ns                             | 0ns <sup>5</sup>                    | Ons <sup>5</sup>         |

|               |          | Kernel Bypass &<br>PCie & Network Stack   | 927ns <= 805Mbps <sup>1</sup>               | 899ns <= 1000Mbps <sup>2</sup>      | 141ns <= 7500Mbps        |

|               |          | Trading<br>Market Data Parsing            | 800ns to 2200ns                             | 36ns                                | 36ns                     |

|               |          | Trading<br>Exchange Communication         | Native Protocol                             | Custom API <sup>3a</sup>            | Custom API <sup>3b</sup> |

|               | External | Broker<br>Validation & Risk Checks        | 350ns <sup>4a</sup> to 1200ns <sup>4b</sup> | 0ns <sup>5</sup>                    | Ons <sup>5</sup>         |

|               |          | OSI Layer 2/3/4<br>Expanded Functionality | 800ns to 3600ns                             | 0ns <sup>5</sup>                    | Ons <sup>5</sup>         |

|               |          | Total Latency                             | 3827ns to 9527ns                            | 935ns                               | 177ns                    |

<sup>&</sup>lt;sup>1</sup> Non-performant @ 810Mbps and above – insufficient to handle 60%+ of typical market data bursts <sup>2</sup> 976ns <= 3000Mbps – sufficient to handle 99%+ of typical market data bursts <sup>3</sup> a) Reduces message size by 50%+ (depending on protocol) significantly improving PCIe transfer; b) PCIe transfer eliminated <sup>4</sup> As Claimed: a) Fusion Raptor; b) Fixnetix i-Execute <sup>5</sup> Conducted in-parallel with network stack functions resulting in zero practical/effective latency <sup>6</sup> US Patents 9,501,795, 10,269,071, 10,868,707, 10,880,211; Others Pending

Not STAC Benchmarks

#### Deploy Your Resources To Focus On Differentiating Competitive Advantages

# It Does What It Says On The Tin

# LMS Is Committed To Transparency and Accuracy

At LMS We Create Real Solutions To Resolve Problems

# TaSR™ - Complimentary Time-Limited Use

Xilinx & LMS...

Are Committed To Your Success

Use TaSR™ To Expose Bottlenecks & Identify Opportunities

#### The Global Standard

Ultra-Low-Latency & Ultra-High-Capacity

> Venue Access & Connectivity

# lets.talk@liquid-markets.com

US: +1-212-784-6145

JP: +81-(0)50-5539-9608

SG: +65-8515-8557